-

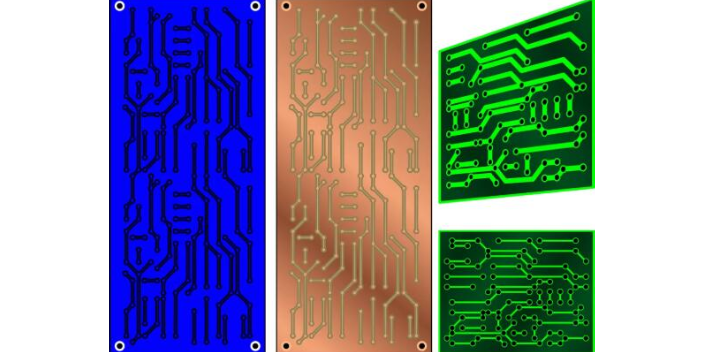

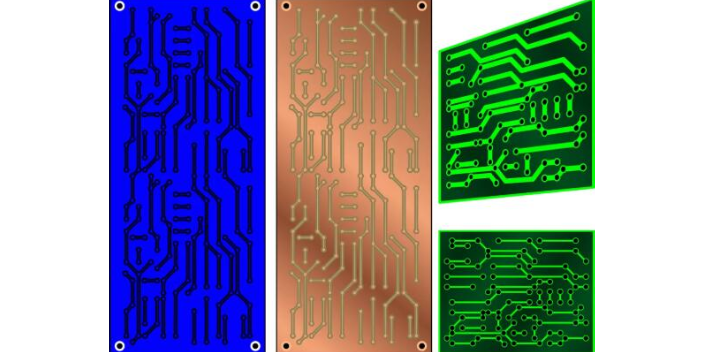

黃岡打造PCB制版廠家

黃岡打造PCB制版廠家從智能手機到人工智能設(shè)備,每一款創(chuàng)新科技產(chǎn)品的背后都離不開PCB的支持。未來,隨著5G、物聯(lián)網(wǎng)和智能制造等新興技術(shù)的發(fā)展,PCB制板的應(yīng)用前景將會更加廣闊,技術(shù)要求也將不斷提高。總之,PCB制板不僅*是一項技術(shù),更是一門結(jié)合了深厚理論與實踐經(jīng)驗的藝術(shù)。它的美在...

2025-07-13 -

荊門高速PCB制板價格大全

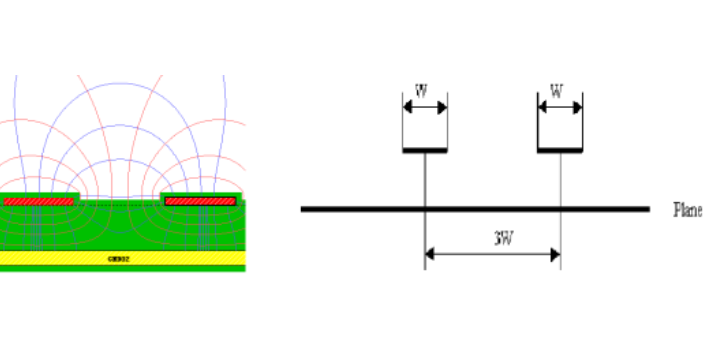

荊門高速PCB制板價格大全阻抗控制在高速信號場景(如USB 3.0、HDMI)中,需通過仿真設(shè)計線寬/線距/介電常數(shù),將阻抗偏差控制在±5%以內(nèi)。散熱設(shè)計高功率器件區(qū)域需增加銅厚(≥2oz)或埋入銅塊,降低熱阻。鋁基板等金屬基材可將熱導(dǎo)率提升至1-3W/mK,較FR-4提升10倍以上。...

2025-07-13 -

如何PCB設(shè)計價格大全

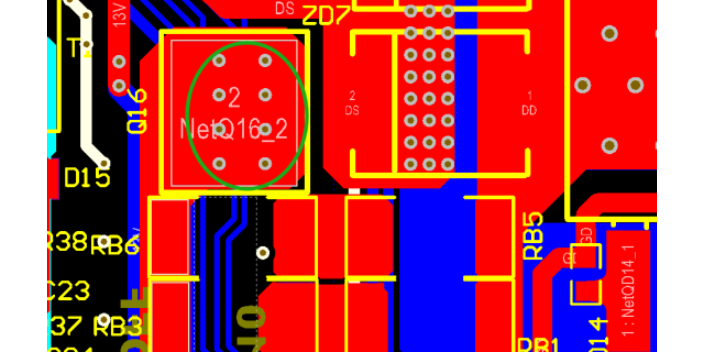

如何PCB設(shè)計價格大全**模塊:軟件工具與行業(yè)規(guī)范的深度融合EDA工具應(yīng)用Altium Designer:適合中小型項目,需掌握原理圖庫管理、PCB層疊設(shè)計、DRC規(guī)則檢查等模塊。例如,通過“交互式布線”功能可實時優(yōu)化走線拓?fù)洌苊怃J角與stub線。Cadence Allegro:...

2025-07-13 -

荊門高速PCB制板銷售電話

荊門高速PCB制板銷售電話PCB制版的關(guān)鍵技術(shù)要點線路精度隨著電子產(chǎn)品小型化,線路寬度和間距不斷縮小(如0.1mm以下),需高精度曝光和蝕刻設(shè)備。層間對位多層板層間對位精度要求高,通常需使用X-Ray鉆孔和光學(xué)對位系統(tǒng)。阻抗控制高速信號傳輸需控制線路阻抗(如50Ω、75Ω),需精確控制...

2025-07-13 -

鄂州常規(guī)PCB設(shè)計布局

鄂州常規(guī)PCB設(shè)計布局常見問題與解決方案地彈噪聲(Ground Bounce)原因:芯片引腳同時切換導(dǎo)致地電位波動。解決:增加去耦電容、優(yōu)化地平面分割、降低電源阻抗。反射與振鈴原因:阻抗不匹配或走線過長。解決:端接電阻匹配(串聯(lián)/并聯(lián))、縮短關(guān)鍵信號走線長度。熱應(yīng)力導(dǎo)致的焊盤脫落原...

2025-07-13 -

襄陽正規(guī)PCB設(shè)計怎么樣

襄陽正規(guī)PCB設(shè)計怎么樣PCB設(shè)計注意事項:從基礎(chǔ)規(guī)范到避坑指南PCB設(shè)計是硬件產(chǎn)品從理論到落地的關(guān)鍵環(huán)節(jié),其質(zhì)量直接影響電路性能、生產(chǎn)良率及產(chǎn)品壽命。以下是PCB設(shè)計過程中需重點關(guān)注的注意事項,涵蓋布局、布線、EMC、可制造性等**環(huán)節(jié),助力工程師高效避坑。布局階段:功能分區(qū)與散熱...

2025-07-13 -

荊門專業(yè)PCB制版批發(fā)

荊門專業(yè)PCB制版批發(fā)隨著智能化、網(wǎng)絡(luò)化的浪潮席卷全球,PCB的應(yīng)用領(lǐng)域也日益***。在物聯(lián)網(wǎng)、人工智能、5G通信等新興技術(shù)的推動下,PCB行業(yè)將迎來巨大的發(fā)展機遇。因此,培訓(xùn)制版已經(jīng)不僅*是為了技能的掌握,更是為將來的職業(yè)發(fā)展鋪平道路。總之,PCB培訓(xùn)制版是一項充滿挑戰(zhàn)與機遇的學(xué)...

2025-07-13 -

荊州設(shè)計PCB設(shè)計怎么樣

荊州設(shè)計PCB設(shè)計怎么樣PCB設(shè)計是一個綜合性的工作,涉及電氣、機械、熱學(xué)等多方面知識,旨在實現(xiàn)電子電路的功能并確保其可靠運行。以下是PCB設(shè)計的主要內(nèi)容:一、前期規(guī)劃需求分析功能需求:明確電路板需要實現(xiàn)的具體功能,例如是用于數(shù)據(jù)采集、信號處理還是電源控制等。以設(shè)計一個簡單的溫度監(jiān)測...

2025-07-13 -

隨州如何PCB設(shè)計

隨州如何PCB設(shè)計PCB培訓(xùn)的**目標(biāo)在于構(gòu)建“原理-工具-工藝-優(yōu)化”的全鏈路能力。初級階段需掌握電路原理圖與PCB布局布線規(guī)范,理解元器件封裝、信號完整性(SI)及電源完整性(PI)的基礎(chǔ)原理。例如,高速信號傳輸中需遵循阻抗匹配原則,避免反射與串?dāng)_;電源層與地層需通過合理分...

2025-07-13 -

隨州高速PCB制板

隨州高速PCB制板PCB布局:將原理圖中的元件合理地放置在PCB板上。布局時要考慮元件之間的電氣性能、散熱、電磁兼容性(EMC)等因素。比如,高頻元件應(yīng)盡量靠近,以減少信號傳輸?shù)难舆t和干擾;發(fā)熱量大的元件要合理安排散熱空間,避免過熱影響性能。布線:根據(jù)布局,在PCB板上進行電氣...

2025-07-13 -

咸寧PCB制板加工

咸寧PCB制板加工外層制作:與內(nèi)層制作流程類似,包括外層干菲林、圖形電鍍、堿性蝕刻等工序,將孔和線路銅層加鍍到一定的厚度,以滿足**終PCB板成品銅厚的要求。樹脂塞孔和樹脂打磨:避免短路和空焊,對PCB板上的孔洞進行清潔和預(yù)處理后鍍銅,再使用樹脂材料填充孔洞,表面磨平后再次鍍銅...

2025-07-12 -

孝感哪里的PCB設(shè)計怎么樣

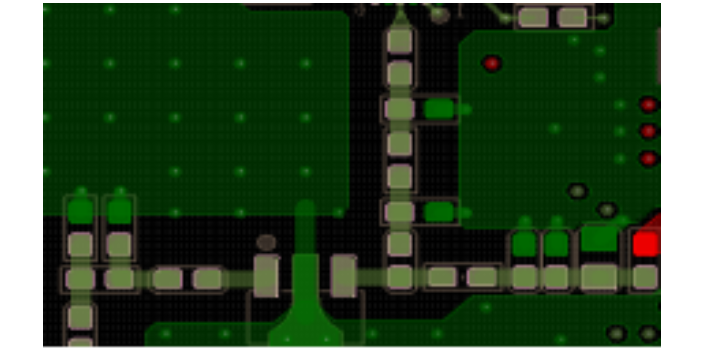

孝感哪里的PCB設(shè)計怎么樣設(shè)計規(guī)則檢查(DRC)運行DRC檢查內(nèi)容:線寬、線距是否符合規(guī)則。過孔是否超出焊盤或禁止布線區(qū)。阻抗控制是否達(dá)標(biāo)。示例:Altium Designer中通過Tools → Design Rule Check運行DRC。修復(fù)DRC錯誤常見問題:信號線與焊盤間距不...

2025-07-12 -

咸寧高速PCB設(shè)計

咸寧高速PCB設(shè)計制造規(guī)則:考慮PCB制造工藝的限制,設(shè)置**小線寬、**小線距、最小孔徑等制造規(guī)則,以保證電路板能夠順利制造。設(shè)計規(guī)則檢查(DRC)***檢查:運行DRC功能,對PCB布局布線進行***檢查,找出違反設(shè)計規(guī)則的地方,并及時進行修改。多次迭代:DRC檢查可能需要...

2025-07-12 -

十堰生產(chǎn)PCB制板功能

十堰生產(chǎn)PCB制板功能接下來,使用顯影液將未固化的油墨清洗掉,露出基材表面。隨后,通過蝕刻工藝,將暴露在外的銅箔腐蝕掉,只留下固化油墨保護下的銅線路,這樣就形成了內(nèi)層線路的雛形。蝕刻過程需要嚴(yán)格控制蝕刻液的濃度、溫度和蝕刻時間,以確保線路的精度和側(cè)壁的垂直度。完成蝕刻后,還需要去除...

2025-07-12 -

恩施正規(guī)PCB設(shè)計多少錢

恩施正規(guī)PCB設(shè)計多少錢PCB設(shè)計是電子工程中的重要環(huán)節(jié),涉及電路原理圖設(shè)計、元器件布局、布線、設(shè)計規(guī)則檢查等多個步驟,以下從設(shè)計流程、設(shè)計規(guī)則、設(shè)計軟件等方面展開介紹:一、設(shè)計流程原理圖設(shè)計:使用EDA工具(如Altium Designer、KiCad、Eagle)繪制電路原理圖,...

2025-07-12 -

荊州常規(guī)PCB設(shè)計功能

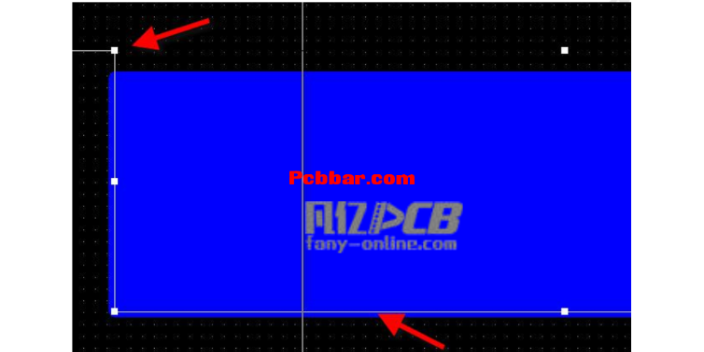

荊州常規(guī)PCB設(shè)計功能PCB布局設(shè)計導(dǎo)入網(wǎng)表與元器件擺放將原理圖網(wǎng)表導(dǎo)入PCB設(shè)計工具,并初始化元器件位置。布局原則:按功能分區(qū):將相關(guān)元器件(如電源、信號處理、接口)集中擺放。信號流向:從輸入到輸出,減少信號線交叉。熱設(shè)計:高功耗元器件(如MOS管、LDO)靠近散熱區(qū)域或添加散熱...

2025-07-12 -

武漢了解PCB設(shè)計哪家好

武漢了解PCB設(shè)計哪家好設(shè)計工具與資源EDA工具:AltiumDesigner:適合中小型項目,操作便捷。CadenceAllegro:適用于復(fù)雜高速設(shè)計,功能強大。KiCad:開源**,適合初學(xué)者和小型團隊。設(shè)計規(guī)范:參考IPC標(biāo)準(zhǔn)(如IPC-2221、IPC-2222)和廠商工藝...

2025-07-12 -

武漢了解PCB設(shè)計規(guī)范

武漢了解PCB設(shè)計規(guī)范設(shè)計優(yōu)化建議模塊化設(shè)計:將復(fù)雜電路劃分為功能模塊(如電源模塊、通信模塊),便于調(diào)試和維護。可制造性設(shè)計(DFM):避免設(shè)計過于精細(xì)的線條或間距,確保PCB制造商能夠可靠生產(chǎn)。文檔管理:保留設(shè)計變更記錄和測試數(shù)據(jù),便于后續(xù)迭代和問題追溯。總結(jié)PCB設(shè)計需綜合考慮...

2025-07-12 -

專業(yè)PCB制板怎么樣

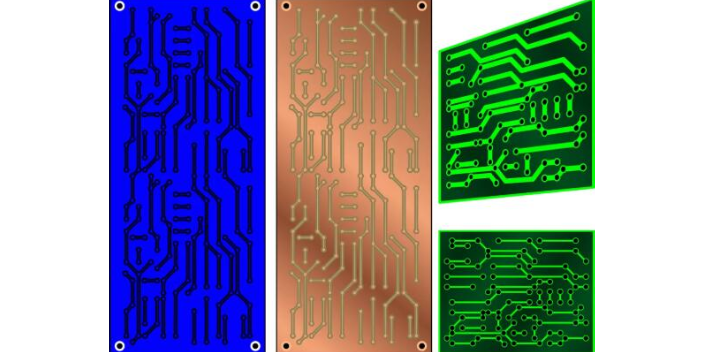

專業(yè)PCB制板怎么樣這些文件就像是PCB的“基因密碼”,包含了制板所需的所有信息,如線路的形狀、尺寸、位置,以及孔的位置、大小等。它們是后續(xù)制板工藝的重要依據(jù),任何細(xì)微的錯誤都可能導(dǎo)致制板失敗或電路性能下降。下料:基材的準(zhǔn)備下料是PCB制板的***道實體工序。根據(jù)設(shè)計要求,選擇合...

2025-07-12 -

隨州高速PCB設(shè)計批發(fā)

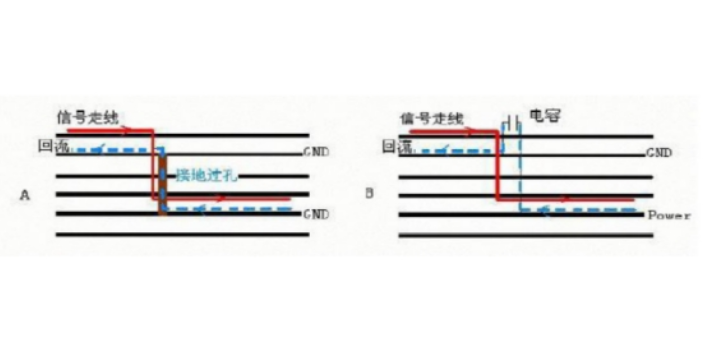

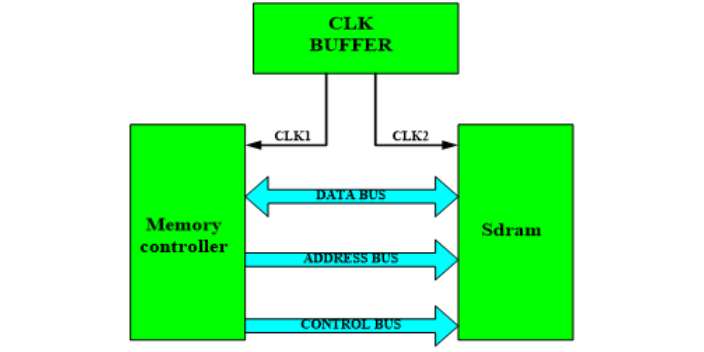

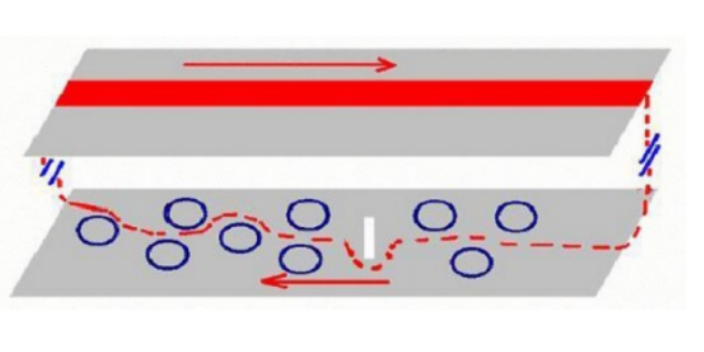

隨州高速PCB設(shè)計批發(fā)關(guān)鍵設(shè)計要素層疊結(jié)構(gòu):PCB的層數(shù)直接影響信號完整性和成本。例如,4層板通常包含信號層、電源層、地層和另一信號層,可有效隔離信號和電源噪聲。多層板設(shè)計需注意層間對稱性,避免翹曲。信號完整性(SI):高速信號(如DDR、USB3.0)需控制傳輸線阻抗(如50Ω或...

2025-07-12 -

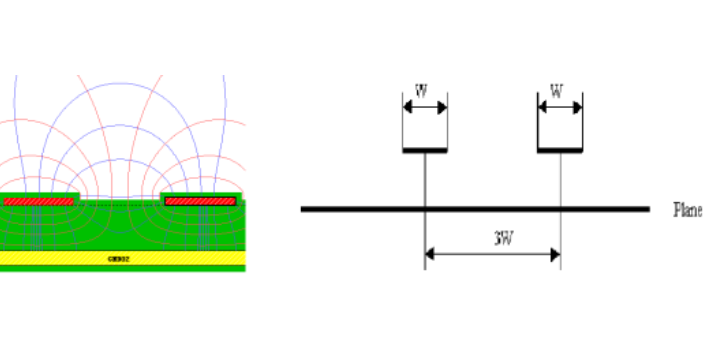

襄陽PCB設(shè)計布局

襄陽PCB設(shè)計布局布局與布線**原則:模塊化布局:按功能分區(qū)(如電源區(qū)、高速信號區(qū)、接口區(qū)),減少耦合干擾。3W原則:高速信號線間距≥3倍線寬,降低串?dāng)_(實測可減少60%以上串?dāng)_)。電源完整性:通過電源平面分割、退耦電容優(yōu)化(0.1μF+10μF組合,放置在芯片電源引腳5mm內(nèi)...

2025-07-12 -

咸寧如何PCB設(shè)計教程

咸寧如何PCB設(shè)計教程PCB設(shè)計是電子工程中的重要環(huán)節(jié),涉及電路原理圖設(shè)計、元器件布局、布線、設(shè)計規(guī)則檢查等多個步驟,以下從設(shè)計流程、設(shè)計規(guī)則、設(shè)計軟件等方面展開介紹:一、設(shè)計流程原理圖設(shè)計:使用EDA工具(如Altium Designer、KiCad、Eagle)繪制電路原理圖,...

2025-07-12 -

焊接PCB制板多少錢

焊接PCB制板多少錢設(shè)計師們運用專業(yè)的EDA(ElectronicDesignAutomation,電子設(shè)計自動化)軟件,如AltiumDesigner、CadenceAllegro等,在虛擬世界中構(gòu)建電路的藍(lán)圖。他們需要根據(jù)產(chǎn)品的功能需求,合理布局各種電子元器件,規(guī)劃信號線和電...

2025-07-12 -

了解PCB制板銷售

了解PCB制板銷售PCB制板相關(guān)內(nèi)容涉及多個關(guān)鍵環(huán)節(jié),以下從基礎(chǔ)概念、材料選擇、制造流程、常見問題及未來趨勢幾個方面展開介紹:一、PCB基礎(chǔ)概念PCB(Printed Circuit Board)即印制電路板,是電子元器件的支撐體和電氣連接的提供者。其按用途可分為焊接用、接插件...

2025-07-12 -

武漢什么是PCB設(shè)計布局

武漢什么是PCB設(shè)計布局總結(jié):以工程思維驅(qū)動設(shè)計升級PCB設(shè)計需平衡電氣性能、可制造性與成本,**策略包括:分層設(shè)計:高速信號層(內(nèi)層)與電源層(外層)交替布局,減少輻射;仿真驅(qū)動:通過SI/PI/EMC仿真提前發(fā)現(xiàn)問題,避免流片失敗;標(biāo)準(zhǔn)化流程:結(jié)合IPC標(biāo)準(zhǔn)與企業(yè)規(guī)范,降低量產(chǎn)風(fēng)...

2025-07-12 -

宜昌打造PCB制板原理

宜昌打造PCB制板原理PCB制板的未來展望材料創(chuàng)新高性能基材:開發(fā)低Dk、低Df、高Tg(玻璃化轉(zhuǎn)變溫度)的材料,如液晶聚合物(LCP)、聚酰亞胺(PI)。功能性材料:如導(dǎo)電油墨、柔性基材(用于可折疊設(shè)備)、嵌入式元件材料等。工藝升級3D打印PCB:通過增材制造技術(shù)實現(xiàn)快速原型制作...

2025-07-12 -

荊門打造PCB制板報價

荊門打造PCB制板報價孔壁鍍層不良:指PCB通孔電鍍過程中,孔內(nèi)銅層出現(xiàn)空洞或不連續(xù),可能由鉆孔質(zhì)量問題、化學(xué)沉銅過程控制不當(dāng)、電鍍參數(shù)不穩(wěn)定等原因?qū)е隆=鉀Q方案包括采用高質(zhì)量的鉆頭并定期更換,優(yōu)化鉆孔參數(shù),嚴(yán)格控制化學(xué)沉銅工藝,調(diào)整電鍍工藝參數(shù)等。短路和開路:短路可能由導(dǎo)體之間的...

2025-07-12 -

孝感了解PCB制板走線

孝感了解PCB制板走線電磁兼容性問題問題表現(xiàn):PCB 產(chǎn)生的電磁輻射超標(biāo),或者對外界電磁干擾過于敏感,導(dǎo)致產(chǎn)品無法通過 EMC 測試。解決方法屏蔽設(shè)計:對于敏感電路或易產(chǎn)生電磁干擾的電路,可以采用金屬屏蔽罩進行屏蔽,減少電磁輻射和干擾。濾波設(shè)計:在電源輸入端、信號接口等位置添加濾波...

2025-07-12 -

黃石了解PCB設(shè)計規(guī)范

黃石了解PCB設(shè)計規(guī)范PCB Layout(印刷電路板布局)是硬件開發(fā)中的**環(huán)節(jié),其質(zhì)量直接影響產(chǎn)品的性能、可靠性和成本。隨著電子設(shè)備向高頻、高速、高密度方向發(fā)展,PCB Layout的復(fù)雜度呈指數(shù)級增長。本文將從設(shè)計原則、關(guān)鍵技巧、常見問題及解決方案等維度展開,結(jié)合***行業(yè)趨...

2025-07-12 -

孝感焊接PCB制板加工

孝感焊接PCB制板加工阻焊油墨和絲印油墨:阻焊油墨用于覆蓋不需要焊接的線路和焊盤,起到絕緣和保護作用;絲印油墨用于在PCB表面印刷元器件標(biāo)識、文字說明等信息。制版工藝流程開料:根據(jù)PCB的設(shè)計尺寸,將覆銅板裁剪成合適的規(guī)格。鉆孔:在覆銅板上鉆出元件安裝孔、導(dǎo)通孔等。鉆孔的精度和質(zhì)量...

2025-07-12